Signal r_ADD_2 : std_logic_vector(c_WIDTH-1 downto 0) := (others => '0')

GEN_CLA : for jj in 0 to g_WIDTH-1 generate GEN_FULL_ADDERS : for ii in 0 to g_WIDTH-1 generate

Signal w_SUM : std_logic_vector(g_WIDTH-1 downto 0) Signal w_C : std_logic_vector(g_WIDTH downto 0) - Carry Signal w_P : std_logic_vector(g_WIDTH-1 downto 0) - Propagate Signal w_G : std_logic_vector(g_WIDTH-1 downto 0) - Generate O_result : out std_logic_vector(g_WIDTH downto 0)Īrchitecture rtl of carry_lookahead_adder is I_add2 : in std_logic_vector(g_WIDTH-1 downto 0) I_add1 : in std_logic_vector(g_WIDTH-1 downto 0) The digital designer simply needs to set the g_WIDTH appropriately for his or her particular application and the tools will generate the correct amount of logic! This code shows how powerful generics and generate statements can be in creating code that is compact, but very scalable. Using the generic, the code creates a generate statement which instantiates as many full-adders as are specified by the g_WIDTH generic. This makes the code more versatile and reusable. The above carry lookahead adder uses a VHDL generic to allow for different implementations of the same code. O_result <= w_C(4) & w_SUM - VHDL ConcatenationĮxample 2: Scalable Carry Lookahead Adder in VHDL Create the Generate (G) Terms: Gi=Ai*Bi

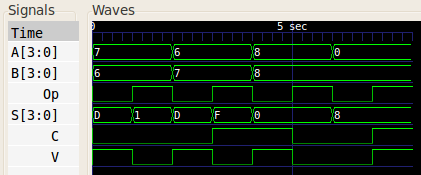

Signal w_SUM : std_logic_vector(3 downto 0) Signal w_C : std_logic_vector(4 downto 0) - Carry Signal w_P : std_logic_vector(3 downto 0) - Propagate Signal w_G : std_logic_vector(3 downto 0) - Generate O_result : out std_logic_vector(4 downto 0)Īrchitecture rtl of carry_lookahead_adder_4_bit is I_add2 : in std_logic_vector(3 downto 0) I_add1 : in std_logic_vector(3 downto 0) As long as inputs to the concatenation operator of the same type they can be concatenated together. The output o_result is assigned using the ampersand (&) VHDL concatenation operator. This is because two N bit vectors added together can produce a result that is N+1 in size. Note that the carry lookahead adder output (o_result) is one bit larger than both of the two adder inputs. VHDL Implementation:Įxample 1: Four-Bit Carry Lookahead Adder in VHDL Therefore it is scalable for any input widths. The second example uses a generic that creates a carry look ahead adder that accepts as an input parameter the WIDTH of the inputs. The first contains a simple carry lookahead adder made up of four full adders (it can add together any four-bit inputs). There are two examples for each VHDL and Verilog shown below. Carry Lookahead Adder 4-bit Block Diagram

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed